### DOCUMENT CHANGE REQUEST

517 DCR number Changes required for: General Originator: S Jeffery - ESCC Date: 2009/05/06 Organisation: ESA/ESTEC Date sent: 2009/05/06 Status: IMPLEMENTED Title: Transistors Silicon Switching PNP, based on type 2N3467 Number: 2 5208/009 Issue: Other documents affected: Page: See attachment Paragraph: See attachment Original wording: Proposed wording: Update the Maximum Ratings table (see the attachment for details) so that this detail spec is clear, complete and the content and format is in-line with other detail specifications for similar Part Types. Justification: Improve the content and clarity of the spec. Attachments: 5208009\_Issue\_3\_-\_Draft\_A.pdf, null Modifications: N/A Approval signature: 12. (c f(an-) Date signed: 2009-05-06

Pages 1 to 13

# TRANSISTORS, SWITCHING, PNP

# **BASED ON TYPE 2N3467**

ESCC Detail Specification No. 5208/009

ESCC Detail Specification No. 5208/009

PAGE 2

ISSUE & 3-Draft A

LEGAL DISCLAIMER AND COPYRIGHT

as apolicable

European Space Agency, Copyright © 2008 All rights reserved.

The European Space Agency disclaims any liability or responsibility, to any person or entity, with respect to any loss or damage caused, or alleged to be caused, directly or indirectly by the use and application of this ESCC publication.

This publication, without the prior permission of the European Space Agency and provided that it is not used for a commercial purpose, may be:

- copied in whole, in any medium, without alteration or modification.

- copied in part, in any medium, provided that the ESCC document identification, comprising the ESCC symbol, document number and document issue, is removed.

### ESCC Detail Specification No. 5208/009

PAGE 3

ISSUE & 3 - Draft A

# **DOCUMENTATION CHANGE NOTICE**

(Refer to https://escies.org for ESCC DCR content)

| ification up issued to inc | corporate editorial a | nd technical char  | nace per DCD    | And 17 - 18 1 1 1 2 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

|----------------------------|-----------------------|--------------------|-----------------|-------------------------------------------------|

|                            | •                     | ina tooriinaar ona | riges per DCh.  |                                                 |

|                            |                       |                    | riges per Dort. |                                                 |

|                            |                       |                    |                 |                                                 |

|                            |                       |                    |                 |                                                 |

### ESCC Detail Specification No. 5208/009

PAGE 6

**ISSUE 2**

At Trase = +25°C

| Characteristics             | Symbols            | Maximum Ratings | Unit | Remarks                           |

|-----------------------------|--------------------|-----------------|------|-----------------------------------|

| Collector-Base Voltage      | V <sub>CBO</sub>   | -40             | V    | Over entire                       |

| Collector-Emitter Voltage   | V <sub>CEO</sub>   | -40             | V    | operating<br>temperature<br>range |

| Emitter-Base Voltage        | V <sub>EBO</sub>   | -5              | V    |                                   |

| Collector Current           | I <sub>C</sub>     | -1              | Α    | Continuous                        |

| Power Dissipation           | P <sub>tot</sub> 1 | 1               | W    | At T <sub>amb</sub> ≤ +25°C       |

|                             | Ptot2              | 5               | W    | -Note-1-                          |

| Operating Temperature Range | T <sub>op</sub>    | -65 to +200     | °C   | Note & 1                          |

| Storage Temperature Range   | T <sub>stg</sub>   | -65 to +200     | °C   | Note % 1                          |

| Soldering Temperature       | T <sub>sol</sub>   | +265            | °C   | Note & 2                          |

So

see attached

#### **NOTES:**

1.—For Tamb>+25°C, derate-linearly to 0W at +200°C

- 1. For Variants with tin-lead plating or hot solder dip lead finish all testing performed at T<sub>amb</sub> > +125°C shall be carried out in a 100% inert atmosphere.

- 2. S. Duration 10 seconds maximum at a distance of not less than 1.5mm from the device body and the same lead shall not be resoldered until 3 minutes have elapsed.

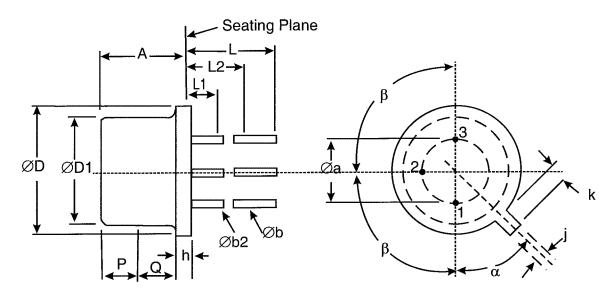

### 1.6 PHYSICAL DIMENSIONS AND TERMINAL IDENTIFICATION

#### 1.6.1 Metal Can Package (TO-39) - 3 lead

| Symbols | Dimension | Notes |        |

|---------|-----------|-------|--------|

|         | Min       | Max   | indies |

| Øa      | 4.83      | 5.35  |        |

| Α       | 6         | 6.6   |        |

| Øb      | 0.4       | 0.533 | 2, 3   |

| Øb2     | 0.4       | 0.483 | 2, 3   |

| Thermal Resistance, |               |     |      |  |

|---------------------|---------------|-----|------|--|

| Junction-to-Ambient | $R_{th(j-a)}$ | 175 | °C/W |  |

| Thermal Resistance, |               |     | ·    |  |

| Junction-to-Case    | $R_{th(j-c)}$ | 30  | °C/W |  |