# DOCUMENT CHANGE REQUEST

378 DCR number Changes required for: N/A Originator: Ron Fidler Date: 2007/10/03 Date sent: 2007/10/03 Organisation: ESA/ESTEC Status: IMPLEMENTED Title: IC Silicon Monolithic, CMOS Static 128k x 8 (131072 x 8 BIT) Asynchronous Random Access Number: 9301/047 Issue: Other documents affected: Page: Re-formated as part of the ongoing conversion to the ECSS editing system. Paragraph: Re-formated as part of the ongoing conversion to the ECSS editing system. Original wording: Proposed wording: The document was in Global-View format with the layout in accordance with the current ECSS format and presentation for 9000 series detail specifications. Therefore, the text is basically unchanged except for correction of a few minor typo errors. In addition, better quality drawings and diagrams have been inserted to make them clear and readable (technically unchanged).

NB: There is known support for active procurement against this specification from the manufacturer ATMEL.

- 1) Title â.. â..Low Power â..added to the title to correctly define the component and the prefix â..Mâ. deleted from the type number to align with current ESCC format for Atmel product.

- 2) 1.4.2 Type Numbers simplified and case references harmonised with manufacturerâ..s own designations.

- 3) 1.5 â.. Amended as follows:-

- ï." Vin lower value rating corrected.

- ï." Vout rating added

- ï." Rth(j-c) rating changed to 3°C/W for both package variants per manufacturer information.

- i." Note 1 expanded to include the functional voltage ranges.

- ï." Note 3 duration and reference to short circuit condition for the IOUT condition removed as these are superfluous.

- 4) 1.7.1 and 1.7.2 Physical Dimensions Drawings harmonised with other Atmel components and related notes updated accordingly.

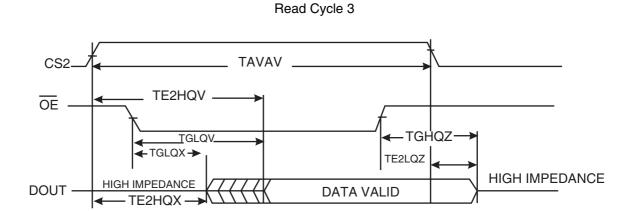

- 5) 1.10 Timing Diagrams- Better quality Read and Write Cycle Timing Diagrams inserted. Sequence of drawing changed

2007-10-03

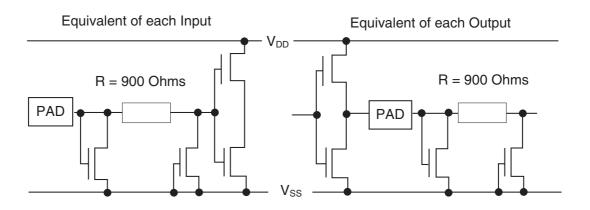

# DOCUMENT CHANGE REQUEST

378 DCR number Changes required for: N/A Originator: Ron Fidler Date: 2007/10/03 Date sent: 2007/10/03 Organisation: ESA/ESTEC Status: IMPLEMENTED and Data Retention Waveform added. 6) 1.12 Protection Networks - Better quality Drawing inserted to enable detail to be clearly read. 7) 2.3.1 Room Temperature Electrical Measurements â.. re-formatted per latest requirements and to harmonise with other Atmel specifications for similar product. Notes amended accordingly. The flow charts and other test pattern definitions removed as these are considered to be adequately controlled by the manufacturerâ..s PID and the QSA, and do not require further definition in the ESCC specification. 8) 2.6 Power Burn-in â.. Definition of test waveforms reformatted to clarify the test conditions. No technical changes made. Justification: AS defined above Attachments: 9301047.pdf, null Modifications: N/A Approval signature: Date signed:

Pages 1 to 22

# INTEGRATED CIRCUITS, SILICON MONOLITHIC, LOW POWER, CMOS 128K X 8 ASYNCHRONOUS STATIC RANDOM ACCESS MEMORY WITH THREE STATE OUTPUTS

# **BASED ON TYPE 65608E**

ESCC Detail Specification No. 9301/047

Issue 2 Draft A September 2007

## LEGAL DISCLAIMER AND COPYRIGHT

European Space Agency, Copyright © 2007. All rights reserved.

The European Space Agency disclaims any liability or responsibility, to any person or entity, with respect to any loss or damage caused, or alleged to be caused, directly or indirectly by the use and application of this ESCC publication.

This publication, without the prior permission of the European Space Agency and provided that it is not used for a commercial purpose, may be:

- copied in whole, in any medium, without alteration or modification.

- copied in part, in any medium, provided that the ESCC document identification, comprising the ESCC symbol, document number and document issue, is removed.

# **DOCUMENTATION CHANGE NOTICE**

(Refer to https://escies.org for ESCC DCR content)

| DCR No | . CHANGE DESCRIPTION                                                           |

|--------|--------------------------------------------------------------------------------|

|        | Specification upissued to incorporate editorial and technical changes per DCR. |

# ESCC Detail Specification No. 9301/047

# ISSUE 2 Draft A

# TABLE OF CONTENTS

| <u>1.</u> | <u>GENERAL</u>                                             | <u>5</u>  |

|-----------|------------------------------------------------------------|-----------|

| 1.1       | Scope                                                      | 5         |

| 1.2       | Applicable Documents                                       | 5         |

| 1.3       | Terms, Definitions, Abbreviations, Symbols and Units       | 5         |

| 1.4       | The ESCC Component Number and Component Type Variants      | 5         |

| 1.4.1     | The ESCC Component Number                                  | 5         |

| 1.4.2     | Component Type Variants                                    | 5         |

| 1.5       | Maximum Ratings                                            | 5         |

| 1.6       | Handling Precautions                                       | 6         |

| 1.7       | Physical Dimensions and Terminal Identification            | 6         |

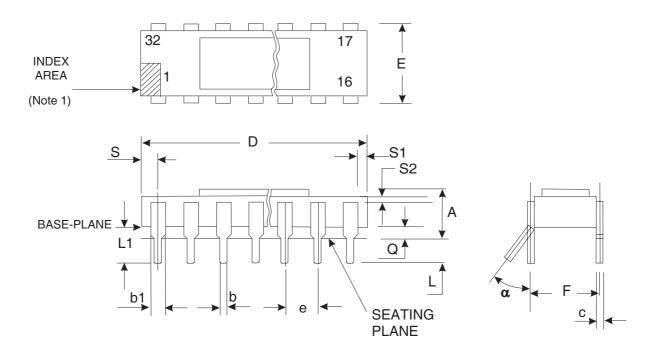

| 1.7.1     | Multilayer Ceramic Dual-in-line Package (MDIL32) - 32 Pin  | 7         |

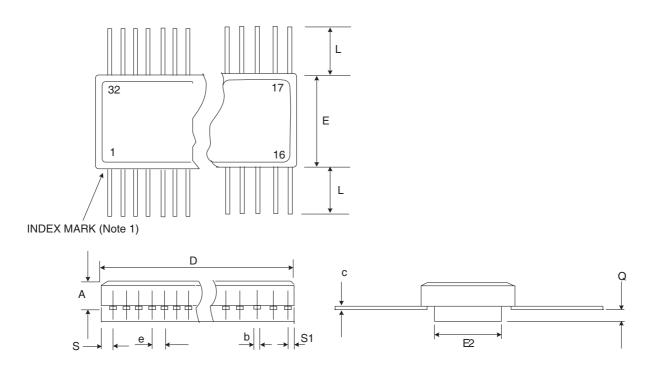

| 1.7.2     | Flat Leaded Multilayer Flat Package (MFP-F32) - 32 Lead    | 8         |

| 1.7.3     | Notes to Physical Dimensions and Terminal Identification   | 8         |

| 1.8       | Functional Diagram                                         | 9         |

| 1.9       | Pin Assignment                                             | 9         |

| 1.10      | Truth Table and Timing Diagrams                            | 10        |

| 1.11      | Protection Networks                                        | 13        |

| <u>2.</u> | REQUIREMENTS                                               | <u>13</u> |

| 2.1       | General                                                    | 13        |

| 2.1.1     | Deviations from the Generic Specification                  | 13        |

| 2.1.1.1   | Deviations from Screening Tests-Chart F3                   | 13        |

| 2.2       | Marking                                                    | 14        |

| 2.3       | Electrical Measurements at Room, High and Low Temperatures | 14        |

| 2.3.1     | Room Temperature Electrical Measurements                   | 14        |

| 2.3.2     | High and Low Temperatures Electrical Measurements          | 20        |

| 2.4       | Parameter Drift Values                                     | 20        |

| 2.5       | Intermediate and End-Point Electrical Measurements         | 21        |

| 2.6       | Power Burn-in Conditions                                   | 22        |

| 2.7       | Operating Life Conditions                                  | 22        |

#### 1. GENERAL

#### 1.1 SCOPE

This specification details the ratings, physical and electrical characteristics and test and inspection data for the component type variants and/or the range of components specified below. It supplements the requirements of, and shall be read in conjunction with, the ESCC Generic Specification listed under Applicable Documents.

#### 1.2 APPLICABLE DOCUMENTS

The following documents form part of this specification and shall be read in conjunction with it:

- (a) ESCC Generic Specification No. 9000

- (b) MIL-STD-883, Test Methods and Procedures for Microelectronics

#### 1.3 TERMS, DEFINITIONS, ABBREVIATIONS, SYMBOLS AND UNITS

For the purpose of this specification, the terms, definitions, abbreviations, symbols and units specified in ESCC Basic Specification No. 21300 shall apply.

#### 1.4 THE ESCC COMPONENT NUMBER AND COMPONENT TYPE VARIANTS

## 1.4.1 <u>The ESCC Component Number</u>

The ESCC Component Number shall be constituted as follows:

Example: 930104701

• Detail Specification Reference: 9301047

Component Type Variant Number: 01 (as required)

## 1.4.2 <u>Component Type Variants</u>

The component type variants applicable to this specification are as follows:

| Variant<br>Number | Based on Type | Access<br>Time<br>(ns) | Case    | Lead/Terminal<br>Material and Finish | Weight<br>max g |

|-------------------|---------------|------------------------|---------|--------------------------------------|-----------------|

| 01                | 65608E-45     | 45                     | MDIL32  | G2                                   | 4.1             |

| 02                | 65608E-45     | 45                     | MFP-F32 | G2                                   | 2.7             |

| 03                | 65608E-30     | 30                     | MDIL32  | G2                                   | 4.1             |

| 04                | 65608E-30     | 30                     | MFP-F32 | G2                                   | 2.7             |

The lead/terminal material and finish shall be in accordance with the requirements of ESCC Basic Specification No. 23500.

#### 1.5 MAXIMUM RATINGS

The maximum ratings shall not be exceeded at any time during use or storage.

Maximum ratings shall only be exceeded during testing to the extent specified in this specification and when stipulated in Test Methods and Procedures of the ESCC Generic Specification.

| Characteristics                                  | Symbols              | Maximum Ratings              | Units | Remarks          |

|--------------------------------------------------|----------------------|------------------------------|-------|------------------|

| Supply Voltage                                   | V <sub>DD</sub>      | -0.5 to 7                    | V     | Note 1           |

| Input Voltage Range                              | V <sub>IN</sub>      | -0.5 to V <sub>DD</sub> +0.3 | V     | Notes 1, 2       |

| Output Voltage Range                             | V <sub>OUT</sub>     | -0.5 to V <sub>DD</sub> +0.3 | V     | Notes 1, 2       |

| Input Current<br>per Signal Pin<br>per Power Pin | I <sub>IN</sub>      | ±10<br>±50                   | mAdc  |                  |

| Output Current (Low)                             | Io                   | ±20                          | mAdc  | Note 3           |

| Device Power<br>Dissipation (Continuous)         | P <sub>D</sub>       | 1                            | W     |                  |

| Operating Temperature Range                      | T <sub>op</sub>      | -55 to +125                  | °C    | T <sub>amb</sub> |

| Storage Temperature Range                        | T <sub>stg</sub>     | -65 to +150                  | °C    |                  |

| Soldering Temperature                            | T <sub>sol</sub>     | +260                         | °C    | Note 4           |

| Junction Temperature                             | Tj                   | +175                         | °C    |                  |

| Thermal Resistance                               | R <sub>th(j-c)</sub> | 3                            | °C/W  |                  |

#### **NOTES:**

- 1. All voltages are with respect to  $V_{SS}$ . Device is functional for  $4.5V \le V_{DD} \le 5.5V$  and for  $-0.5V \le V_{IL} \le 0.8V$ ;  $2.2V \le V_{IH} \le V_{DD} + 0.3V$ .

- 2.  $V_{DD}$  +0.3V shall not exceed 7V.

- 3. The maximum output current of any single output.

- 4. Duration 10 seconds maximum at a distance of not less than 1.6mm from the device body and the same terminal shall not be resoldered until 3 minutes have elapsed.

#### 1.6 HANDLING PRECAUTIONS

These devices are susceptible to damage by electrostatic discharge. Therefore, suitable precautions shall be employed for protection during all phases of manufacture, testing, packaging, shipment and any handling.

These components are categorised as Class 2 with a Minimum Critical Path Failure Voltage of 2000 Volts.

#### 1.7 PHYSICAL DIMENSIONS AND TERMINAL IDENTIFICATION

Consolidated Notes are given following the case drawings and dimensions.

# 1.7.1 <u>Multilayer Ceramic Dual-in-line Package (MDIL32) - 32 Pin</u>

| Symbols | Dimension | Notes |       |

|---------|-----------|-------|-------|

| Symbols | Min       | Max   | Notes |

| Α       | 2.92      | 4.32  | 5     |

| b       | 0.4       | 0.51  | 2     |

| b1      | 0.96      | 1.65  | 2     |

| С       | 0.23      | 0.3   | 2     |

| D       | 40.13     | 41.15 |       |

| E       | 10.16     | 10.67 |       |

| F       | 9.9       | 10.41 | 6     |

| е       | 2.54      | BSC   | 2, 3  |

| L       | 3.43      | 4.2   | 2, 5  |

| L1      | 4.44      | 5.72  | 2     |

| Q       | 1.02      | 1.52  | 2     |

| S       | -         | 1.65  | 8     |

| S1      | 0.13      | -     | 8     |

| S2      | 0.13      | -     | 2     |

| α       | 0°        | 15°   | 2     |

## 1.7.2 <u>Flat Leaded Multilayer Flat Package (MFP-F32) - 32 Lead</u>

| Symbols | Dimension | Notes |       |

|---------|-----------|-------|-------|

| Symbols | Min       | Max   | Notes |

| Α       | 1.78      | 2.72  |       |

| b       | 0.38      | 0.48  | 2     |

| С       | 0.076     | 0.15  | 2     |

| D       | 20.62     | 21.03 | 7     |

| Е       | 10.26     | 10.57 | 7     |

| E2      | 6.96      | 7.26  |       |

| е       | 1.27      | BSC   | 2, 4  |

| L       | 7.37      | 7.87  | 2     |

| Q       | 0.51      | 0.76  | 2, 9  |

| S       | -         | 1.14  | 8     |

| S1      | 0         | -     | 8     |

# 1.7.3 <u>Notes to Physical Dimensions and Terminal Identification</u>

- 1. Index mark: a notch or terminal 1 identification mark for MFP-F32 package shall be located adjacent to terminal 1 and for MDIL32 shall be in the shaded area.

- 2. All terminals.

- 3. 30 places. The true position pin spacing is 2.54mm between centrelines. Each pin centreline shall be located within ±0.25mm of its true longitudinal position relative to Pin 1 and the highest pin number

- 4. 30 places. The true position pin spacing is 1.27mm between centrelines. Each pin centreline shall be located within  $\pm 0.13$ mm of its true longitudinal position relative to Pin 1 and the highest pin

number.

- 5. Dimensions are measured with the package seated in a seating plane gauge.

- 6. Dimensions are measured with the leads constrained to be perpendicular to the base plane.

- 7. This dimension allows for package edge anomalies caused by material protrusions, such as rough ceramic, misaligned ceramic layers and lids, meniscus, and glass overrun.

The corner shape (square, notch, radius etc.) may vary at the manufacturer's option from that shown on the drawing.

- 8. Two places.

- 9. Dimension shall be measured at the point of exit of the lead from the body.

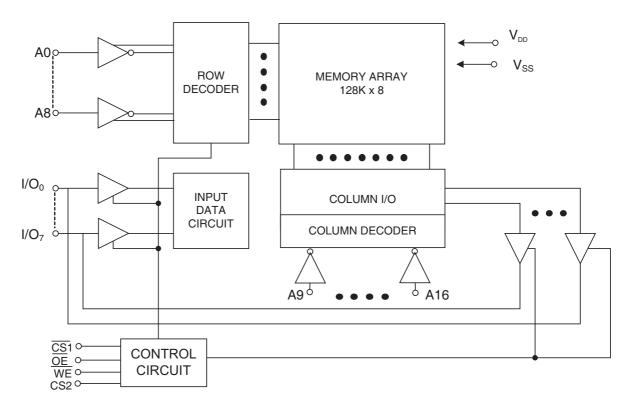

## 1.8 <u>FUNCTIONAL DIAGRAM</u>

## 1.9 PIN ASSIGNMENT

| Pin | Function            |

|-----|---------------------|

| 1   | Not Connected       |

| 2   | A16 Input (Address) |

| 3   | A14 Input (Address) |

| 4   | A12 Input (Address) |

| 5   | A7 Input (Address)  |

| 6   | A6 Input (Address)  |

| 7   | A5 Input (Address)  |

| Pin | Function                 |

|-----|--------------------------|

| 8   | A4 Input (Address)       |

| 9   | A3 Input (Address)       |

| 10  | A2 Input (Address)       |

| 11  | A1 Input (Address)       |

| 12  | A0 Input (Address)       |

| 13  | I/O0 Input/Output (Data) |

| 14  | I/O1 Input/Output (Data) |

| 15  | I/O2 Input/Output (Data) |

| 16  | V <sub>SS</sub>          |

| 17  | I/O3 Input/Output (Data) |

| 18  | I/O4 Input/Output (Data) |

| 19  | I/O5 Input/Output (Data) |

| 20  | I/O6 Input/Output (Data) |

| 21  | I/O7 Input/Output (Data) |

| 22  | CS1 Input (Chip Select)  |

| 23  | A10 Input (Address)      |

| 24  | OE Input (Output Enable) |

| 25  | A11 Input (Address)      |

| 26  | A9 Input (Address)       |

| 27  | A8 Input (Address)       |

| 28  | A13 Input (Address)      |

| 29  | WE Input (Write Enable)  |

| 30  | CS2 Input (Chip Select)  |

| 31  | A15 Input (Address)      |

| 32  | V <sub>DD</sub>          |

# 1.10 TRUTH TABLE AND TIMING DIAGRAMS

1. Logic Level Definitions: L = Low Level, H = High Level, X = Irrelevant and Z = High Impedance.

|                 | Inputs       |   | Inputs Inputs/Outputs |          | Mode                  |

|-----------------|--------------|---|-----------------------|----------|-----------------------|

| CS <sub>1</sub> | S1 CS2 WE OE |   | I/On                  |          |                       |

| Н               | Х            | Х | Х                     | Z        | Deselected/Power Down |

| Х               | L            | Х | Х                     | Z        | Deselected/Power Down |

| L               | Н            | Н | L                     | Data out | Read                  |

| L               | Н            | L | Х                     | Data in  | Write                 |

| L               | Н            | Н | Н                     | Z        | Output Disable        |

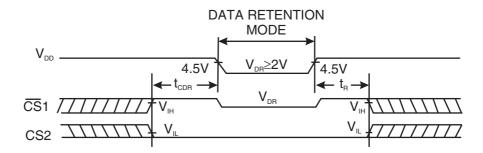

## **Data Retention**

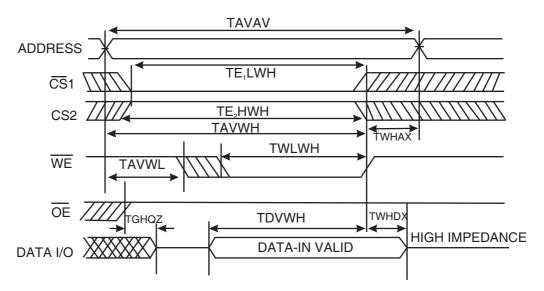

Write Cycle 1: WE controlled, OE High during Write (Note 1)

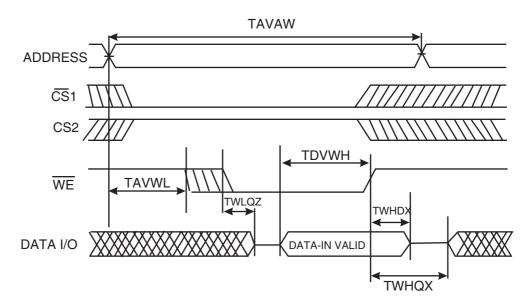

Write Cycle 2 : WE controlled , OE Low (Note 1)

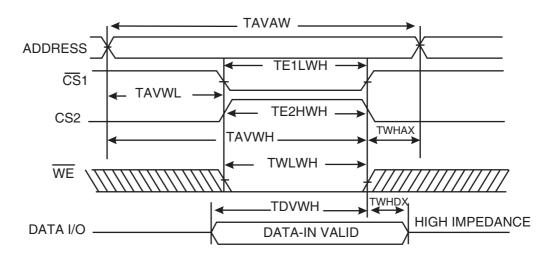

Write Cycle 3: CS1 or CS2 controlled (Note 1)

# **NOTES:**

The internal write time of the memory is defined by the overlap of  $\overline{CS}1$  Low and CS2 High and  $\overline{WE}$  Low. Both signals must be activated to initiate a write and either signal can terminate a write by going inactive. The data input setup and hold timing should be referenced to the active edge of the signal that terminates the write. Data out is high impedance if  $\overline{OE} = V_{IH}$ .

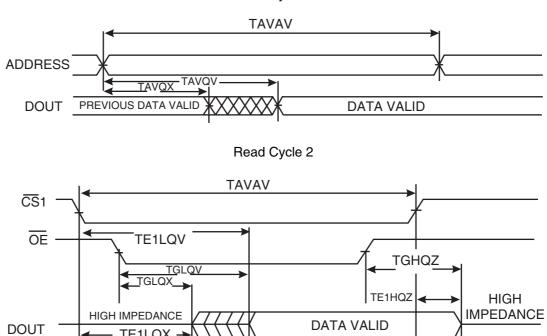

Read Cycle 1

## 1.11 PROTECTION NETWORKS

## 2. REQUIREMENTS

## 2.1 GENERAL

The complete requirements for procurement of the components specified herein are as stated in this specification and the ESCC Generic Specification. Permitted deviations from the Generic Specification, applicable to this specification only, are listed below.

Permitted deviations from the Generic Specification and this Detail Specification, formally agreed with specific Manufacturers on the basis that the alternative requirements are equivalent to the ESCC requirement and do not affect the component's reliability, are listed in the appendices attached to this specification.

# 2.1.1 <u>Deviations from the Generic Specification</u>

## 2.1.1.1 Deviations from Screening Tests-Chart F3

(a) High Temperature Reverse Bias Burn-in shall not be performed.

#### 2.2 MARKING

The marking shall be in accordance with the requirements of ESCC Basic Specification No. 21700 and as follows.

The information to be marked on the component shall be:

- (a) Terminal identification.

- (b) The ESCC qualified components symbol (for ESCC qualified components only).

- (c) The ESCC Component Number.

- (d) Traceability information.

# 2.3 <u>ELECTRICAL MEASUREMENTS AT ROOM, HIGH AND LOW TEMPERATURES</u>

Electrical measurements shall be performed at room, high and low temperatures.

## 2.3.1 Room Temperature Electrical Measurements

The measurements shall be performed at  $T_{amb}$ =+22 ±3°C.

| Characteristics                                                   | Symbols           | MIL-STD-883 | Test Conditions                                                                                                                   | Limits |     | Units |

|-------------------------------------------------------------------|-------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------|--------|-----|-------|

|                                                                   |                   | Test Method | Note 1                                                                                                                            | Min    | Max |       |

| Functional Test 1                                                 | -                 | 3014        | Verify Truth Table<br>Note 2                                                                                                      | -      | -   | -     |

| Functional Test 2                                                 | -                 | 3014        | Verify Truth Table<br>Note 2                                                                                                      | -      | -   | -     |

| Functional Test 3                                                 | -                 | 3014        | Verify Truth Table<br>Note 2                                                                                                      | -      | -   | -     |

| Functional Test 4                                                 | -                 | 3014        | Verify Truth Table<br>Note 2                                                                                                      | -      | -   | -     |

| Input Clamp<br>Voltage, to V <sub>SS</sub>                        | V <sub>IC</sub>   | 3008        | I <sub>IN</sub> (Under Test)=<br>-100μA<br>All Other Pins Open<br>V <sub>DD</sub> = Open,V <sub>SS</sub> =0V                      | -0.2   | -2  | V     |

| Low Level Input<br>Current                                        | I <sub>IL</sub>   | 3009        | V <sub>IN</sub> (Under Test)=0V<br>V <sub>IN</sub> (Remaining<br>Inputs)=5.5V<br>V <sub>DD</sub> =5.5V, V <sub>SS</sub> =0V       | -      | -1  | μΑ    |

| High Level Input<br>Current                                       | ІІН               | 3010        | V <sub>IN</sub> (Under Test)=5.5V<br>V <sub>IN</sub> (Remaining<br>Inputs)=0V<br>V <sub>DD</sub> =5.5V, V <sub>CC</sub> =5.5V     | -      | 1   | μА    |

| Output Leakage<br>Current, Third<br>State, Low Level<br>Applied 1 | I <sub>OZL1</sub> | 3020        | V <sub>IN</sub> (CS1)=5V<br>V <sub>IN</sub> (CS2)=0V<br>V <sub>IN</sub> (Output)=0V<br>V <sub>DD</sub> =5.5V, V <sub>SS</sub> =0V | -      | -1  | μА    |

| Characteristics                                                    | Symbols            | MIL-STD-883 | Test Conditions                                                                                                                                                                                                                                                         | Lin | nits | Units |

|--------------------------------------------------------------------|--------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-------|

|                                                                    |                    | Test Method | Note 1                                                                                                                                                                                                                                                                  | Min | Max  |       |

| Output Leakage<br>Current, Third<br>State, Low Level<br>Applied 2  | I <sub>OZL2</sub>  | 3020        | $ \begin{array}{c} V_{IN}(\overline{CS}1) {=} 0V \\ V_{IN}(CS2) {=} 5V \\ V_{IN}(\overline{WE}, \overline{OE}) {=} 5V \\ V_{IN}(Output) {=} 0V \\ V_{DD} {=} 5.5V, V_{SS} {=} 0V \end{array} $                                                                          | -   | -1   | μА    |

| Output Leakage<br>Current, Third<br>State, High Level<br>Applied 1 | I <sub>OZH1</sub>  | 3021        | $V_{IN}(\overline{CS}1)=5V$<br>$V_{IN}(CS2)=0V$<br>$V_{IN}(Output)=5.5V$<br>$V_{DD}=5.5V, V_{SS}=0V$                                                                                                                                                                    | -   | 1    | μА    |

| Output Leakage<br>Current, Third<br>State, High Level<br>Applied 2 | I <sub>OZH2</sub>  | 3021        | $V_{IN}(\overline{CS}1)=0V$<br>$V_{IN}(CS2)=5V$ ,<br>$V_{IN}(\overline{WE}, \overline{OE})=5V$<br>$V_{IN}(Output)=5.5V$<br>$V_{DD}=5.5V$ , $V_{SS}=0V$                                                                                                                  | -   | 1    | μА    |

| Low Level Output<br>Voltage                                        | V <sub>OL</sub>    | 3007        | $\begin{array}{c} \text{V}_{\text{IL}}\text{=}0.8\text{V},\text{V}_{\text{IH}}\text{=}2.2\text{V} \\ \text{I}_{\text{OL}}\text{=}8\text{mA} \\ \text{V}_{\text{DD}}\text{=}4.5\text{V},\text{V}_{\text{SS}}\text{=}0\text{V} \\ \text{Note 3} \end{array}$              | -   | 400  | mV    |

| High Level Output<br>Voltage                                       | V <sub>OH</sub>    | 3006        | V <sub>IL</sub> =0.8V, V <sub>IH</sub> =2.2V<br>I <sub>OH</sub> =-4mA<br>V <sub>DD</sub> =4.5V, V <sub>SS</sub> =0V<br>Note 4                                                                                                                                           | 2.4 | -    | V     |

| Stand-by Supply<br>Current 1                                       | I <sub>DDSB1</sub> | 3005        | $\begin{array}{c} V_{IL} = 0.8 \text{V, } V_{IH} = 2.2 \text{V} \\ V_{IN}(\overline{\text{CS}}1) = 2.2 \text{V} \\ V_{IN}(\text{CS2}) = 0.8 \text{V} \\ \text{f=0Hz} \\ V_{DD} = 5.5 \text{V, } V_{SS} = 0 \text{V} \\ \text{Note 5} \end{array}$                       | -   | 2    | mA    |

| Stand-by Supply<br>Current 2                                       | I <sub>DDSB2</sub> | 3005        | $\begin{array}{c} V_{IL} {=} 0.8 \text{V, } V_{IH} {=} 2.2 \text{V} \\ V_{IN}(\overline{\text{CS}}1) {=} 5.2 \text{V} \\ V_{IN}(\text{CS2}) {=} 0 \text{V} \\ \text{f} {=} 0 \text{Hz} \\ V_{DD} {=} 5.5 \text{V, } V_{SS} {=} 0 \text{V} \\ \text{Note 5} \end{array}$ | -   | 300  | μА    |

| Dynamic<br>Operating Supply<br>Current                             | I <sub>DDOP</sub>  | 3005        | $\begin{array}{c} V_{IN}(\overline{WE},\overline{OE},\\ CS2)=2.2V\\ V_{IN}(\overline{CS1})=0.8V\\ V_{IN}(Remaining\\ Inputs)=0.2V\\ I_{OUT}=0A\\ V_{DD}=5.5V,V_{SS}=0V\\ Variants01,02\\ f=22.2MHz \end{array}$                                                         | -   | 100  | mA    |

|                                                                    |                    |             | Variants 03, 04<br>f=33.3MHz                                                                                                                                                                                                                                            | -   | 130  |       |

| Characteristics                       | Symbols           | MIL-STD-883 | Test Conditions                                                                                                                                                           | Lin      | Units    |    |

|---------------------------------------|-------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|----|

|                                       |                   | Test Method | Note 1                                                                                                                                                                    | Min      | Max      | 1  |

| Data Retention<br>Current             | I <sub>DDDR</sub> | 3005        | V <sub>IN</sub> (CS1)=1.8V<br>V <sub>IN</sub> (CS2)=0.2V<br>V <sub>IN</sub> (Remaining<br>Inputs)=0.2V and 1.8V<br>V <sub>DD</sub> =2V, V <sub>SS</sub> =0V<br>Notes 5, 6 | -        | 150      | μА |

| Data Retention<br>Test                | -                 | -           | Note 6                                                                                                                                                                    | -        | -        | -  |

| Input<br>Capacitance                  | C <sub>IN</sub>   | 3012        | V <sub>IN</sub> =V <sub>SS</sub> =0V<br>V <sub>DD</sub> = 0V<br>f= 1MHz<br>Note 7                                                                                         | -        | 8        | pF |

| Output<br>Capacitance                 | C <sub>OUT</sub>  | 3012        | V <sub>IN</sub> =V <sub>SS</sub> =0<br>V <sub>DD</sub> = 0V<br>f= 1MHz<br>Note 7                                                                                          | -        | 8        | pF |

| Read Cycle Time                       | t <sub>AVAV</sub> | 3003        | V <sub>DD</sub> =4.5V & 5.5V<br>V <sub>SS</sub> =0V<br>Note 8<br>Variants 01, 02<br>Variants 03, 04                                                                       | 45<br>30 | -<br>-   | ns |

| Address Access<br>Time                | t <sub>AVQV</sub> | 3003        | $V_{DD}$ =4.5V & 5.5V $V_{SS}$ =0V Note 9 Variants 01, 02 Variants 03, 04                                                                                                 | -        | 45<br>30 | ns |

| Output Change<br>from Address<br>Time | t <sub>AVQX</sub> | 3003        | V <sub>DD</sub> =4.5V & 5.5V<br>V <sub>SS</sub> =0V<br>Note 8                                                                                                             | 5        | -        | ns |

| Write Cycle Time                      | t <sub>AVAW</sub> | 3003        | V <sub>DD</sub> =4.5V & 5.5V<br>V <sub>SS</sub> =0V<br>Note 8<br>Variants 01, 02<br>Variants 03, 04                                                                       | 45<br>30 |          | ns |

| Address Set-up<br>Time                | t <sub>AVWL</sub> | 3003        | V <sub>DD</sub> =4.5V & 5.5V<br>V <sub>SS</sub> =0V<br>Note 8                                                                                                             | 0        | -        | ns |

| Address Valid to<br>End of Write      | t <sub>AVWH</sub> | 3003        | V <sub>DD</sub> =4.5V & 5.5V<br>V <sub>SS</sub> =0V<br>Note 8<br>Variants 01, 02<br>Variants 03, 04                                                                       | 35<br>22 | -<br>-   | ns |

| Data Setup Time                       | t <sub>DVWH</sub> | 3003        | V <sub>DD</sub> =4.5V & 5.5V<br>V <sub>SS</sub> =0V<br>Note 9<br>Variants 01, 02<br>Variants 03, 04                                                                       | 20<br>18 | -<br>-   | ns |

| Characteristics                              | Symbols            | MIL-STD-883 | Test Conditions                                                                                      | Lin      | nits     | Units |

|----------------------------------------------|--------------------|-------------|------------------------------------------------------------------------------------------------------|----------|----------|-------|

|                                              |                    | Test Method | Note 1                                                                                               | Min      | Max      |       |

| Chip Select 1 Low<br>to End of Write         | t <sub>E1LWH</sub> | 3003        | V <sub>CC</sub> =4.5V & 5.5V<br>V <sub>SS</sub> =0V<br>Note 8<br>Variants 01, 02<br>Variants 03, 04  | 35<br>22 | -        | ns    |

| Chip Select 2<br>High to End of<br>Write     | t <sub>E2HWH</sub> | 3003        | V <sub>DD</sub> =4.5V & 5.5V<br>V <sub>SS</sub> =0V<br>Note 8<br>Variants 01, 02<br>Variants 03, 04  | 35<br>22 | -        | ns    |

| Write Enable Low<br>Output Disable<br>Time   | t <sub>WLQZ</sub>  | 3003        | V <sub>DD</sub> =4.5V & 5.5V<br>V <sub>SS</sub> =0V<br>Note 10<br>Variants 01, 02<br>Variants 03, 04 | -        | 15<br>8  | ns    |

| Write Enable Low<br>Pulse Width              | t <sub>WLWH</sub>  | 3003        | V <sub>DD</sub> =4.5V & 5.5V<br>V <sub>SS</sub> =0V<br>Note 9<br>Variants 01, 02<br>Variants 03, 04  | 35<br>22 | -        | ns    |

| Address Hold<br>from End of Write<br>Time    | t <sub>WHAX</sub>  | 3003        | V <sub>DD</sub> =4.5V & 5.5V<br>V <sub>SS</sub> =0V<br>Note 8                                        | 0        | -        | ns    |

| Data Hold Time                               | t <sub>WHDX</sub>  | 3003        | V <sub>DD</sub> =4.5V & 5.5V<br>V <sub>SS</sub> =0V<br>Note 9                                        | 0        | -        | ns    |

| Write Enable High<br>Output Enable<br>Time   | t <sub>WHQX</sub>  | 3003        | V <sub>DD</sub> =4.5V & 5.5V<br>V <sub>SS</sub> =0V<br>Note 10                                       | 0        | -        | ns    |

| Chip Select 1<br>Access Time                 | t <sub>E1LQV</sub> | 3003        | V <sub>DD</sub> =4.5V & 5.5V<br>V <sub>SS</sub> =0V<br>Note 9<br>Variants 01, 02<br>Variants 03, 04  | -        | 45<br>30 | ns    |

| Chip Select 1 Low<br>Output Enable<br>Time   | t <sub>E1LQX</sub> | 3003        | V <sub>DD</sub> =4.5V & 5.5V<br>V <sub>SS</sub> =0V<br>Note 10                                       | 3        | -        | ns    |

| Chip Select 1<br>High Output<br>Disable Time | t <sub>E1HQZ</sub> | 3003        | V <sub>DD</sub> =4.5V & 5.5V<br>V <sub>SS</sub> =0V<br>Note 10<br>Variants 01, 02<br>Variants 03, 04 | -        | 20<br>15 | ns    |

| Chip Select 2<br>Access Time                 | t <sub>E2HQV</sub> | 3003        | V <sub>DD</sub> =4.5V & 5.5V<br>V <sub>SS</sub> =0V<br>Note 9<br>Variants 01, 02<br>Variants 03, 04  | -<br>-   | 45<br>30 | ns    |

| Characteristics                              | Symbols            | MIL-STD-883 | Test Conditions                                                                                        | Lin | nits     | Units |

|----------------------------------------------|--------------------|-------------|--------------------------------------------------------------------------------------------------------|-----|----------|-------|

|                                              |                    | Test Method | Note 1                                                                                                 | Min | Max      |       |

| Chip Select 2<br>High Output<br>Enable Time  | t <sub>E2HQX</sub> | 3003        | V <sub>DD</sub> =4.5V & 5.5V<br>V <sub>SS</sub> =0V<br>Note 10                                         | 3   | -        | ns    |

| Chip Select 2 Low<br>Output Disable<br>Time  | t <sub>E2LQZ</sub> | 3003        | V <sub>DD</sub> =4.5V & 5.5V<br>V <sub>SS</sub> =0V<br>Note 10<br>Variants 01, 02<br>Variants 03, 04   | -   | 20<br>15 | ns    |

| Output Enable<br>Access Time                 | t <sub>GLQV</sub>  | 3003        | V <sub>DD</sub> =4.5V and 5.5V<br>V <sub>SS</sub> =0V<br>Note 8<br>Variants 01, 02<br>Variants 03, 04  | -   | 15<br>12 | ns    |

| Output Enable<br>Low Output<br>Enable Time   | t <sub>GLQX</sub>  | 3003        | V <sub>DD</sub> =4.5V and 5.5V<br>V <sub>SS</sub> =0V<br>Note 10                                       | 0   | -        | ns    |

| Output Enable<br>High Output<br>Disable Time | <sup>t</sup> GHQZ  | 3003        | V <sub>DD</sub> =4.5V and 5.5V<br>V <sub>SS</sub> =0V<br>Note 10<br>Variants 01, 02<br>Variants 03, 04 | -   | 15<br>8  | ns    |

# **NOTES:**

1. Unless otherwise specified all inputs and outputs shall be tested for each characteristic, inputs not

PAGE 19

under test shall be  $V_{\text{IN}} = V_{\text{SS}}$  or  $V_{\text{DD}}$  and outputs not under test shall be open. Functional go-no-go test with the following test sequences:

# **FUNCTIONAL TEST 1**

| Pattern      | Timing<br>(ns)<br>Note (a) | V <sub>DD</sub> (V) | V <sub>SS</sub><br>(V) | V <sub>IL</sub> (V) | V <sub>IH</sub> (V) | I <sub>OL</sub><br>(mA) | I <sub>OH</sub><br>(mA) | V <sub>out comp</sub> (V) Note (c) |

|--------------|----------------------------|---------------------|------------------------|---------------------|---------------------|-------------------------|-------------------------|------------------------------------|

| March        | 105                        | 4.5 & 5.5           | 0                      | 0                   | 3                   | 0.5                     | -0.5                    | 1.5                                |

| Checkerboard | 105                        | 4.5 & 5.5           | 0                      | 0                   | 3                   | 0.5                     | -0.5                    | 1.5                                |

| Imag         | 105                        | 4.5 & 5.5           | 0                      | 0                   | 3                   | 0.5                     | -0.5                    | 1.5                                |

#### **FUNCTIONAL TEST 2**

| Pattern | Timing<br>(ns)<br>Note (a) | V <sub>DD</sub><br>(V) | V <sub>SS</sub> (V) | V <sub>IL</sub><br>(mV) | V <sub>IH</sub><br>(V) | I <sub>OL</sub><br>(mA) | I <sub>OH</sub><br>(mA) | V <sub>out comp</sub> (V) Note (c) |

|---------|----------------------------|------------------------|---------------------|-------------------------|------------------------|-------------------------|-------------------------|------------------------------------|

| March   | 105                        | 5.5                    | 0                   | -300                    | 5.8                    | 0.5                     | -0.5                    | 1.5                                |

| March   | 105                        | 4.5                    | 0                   | -300                    | 4.8                    | 0.5                     | -0.5                    | 1.5                                |

| March   | 105                        | 5.5                    | 0                   | 0                       | 2.2                    | 0.5                     | -0.5                    | 1.5                                |

| March   | 105                        | 4.5                    | 0                   | 800                     | 3                      | 0.5                     | -0.5                    | 1.5                                |

#### **FUNCTIONAL TEST 3**

| Pattern | Timing<br>(ns)<br>Note (a) | V <sub>DD</sub> (V) | V <sub>SS</sub><br>(V) | V <sub>IL</sub> (V) | V <sub>IH</sub> (V) | I <sub>OL</sub><br>(mA) | I <sub>OH</sub> (mA) | V <sub>out comp</sub> (V) Note (c) |

|---------|----------------------------|---------------------|------------------------|---------------------|---------------------|-------------------------|----------------------|------------------------------------|

| March   | 105                        | 4.5                 | 0                      | 0                   | 3                   | 8                       | -4                   | Note (b)                           |

| Genbl   | 105                        | 4.5                 | 0                      | 0                   | 3                   | 0.5                     | -0.5                 | 1.5                                |

# **FUNCTIONAL TEST 4**

| Pattern           | Timing (ns) Note (a) Variant |        | V <sub>DD</sub><br>(V) | V <sub>SS</sub><br>(V) | V <sub>IL</sub><br>(V) | V <sub>IH</sub> (V) | I <sub>OL</sub><br>(mA) | I <sub>OH</sub><br>(mA) | V <sub>out comp</sub> (V) Note (c) |

|-------------------|------------------------------|--------|------------------------|------------------------|------------------------|---------------------|-------------------------|-------------------------|------------------------------------|

|                   | 01, 02                       | 03, 04 |                        |                        |                        |                     |                         |                         |                                    |

| March/Comarch     | 115                          | 90     | 4.5                    | 0                      | 0                      | 3                   | 0.5                     | -0.5                    | 1.5                                |

| Imag/Checkerboard | 115                          | 90     | 4.5                    | 0                      | 0                      | 3                   | 0.5                     | -0.5                    | 1.5                                |

| March/Comarch     | 115                          | 90     | 4.5                    | 0                      | 0                      | 3                   | 0.5                     | -0.5                    | 1.5                                |

| Imag/Checkerboard | 115                          | 90     | 4.5                    | 0                      | 0                      | 3                   | 0.5                     | -0.5                    | 1.5                                |

- (a) A write cycle is followed by a read cycle. The time between start of write and start of read per the truth table is the specified timing parameter.  $t_r = t_f \le 5$ ns.

- (b) 0.4V for low output level, 2.4V for high output level.

- (c) Output load 1 TTL gate equivalent  $+C_L < 30pF$ .

- Select address inputs to produce a low level at the pin under test.

- Select address inputs to produce a high level at the pin under test.

- Measurements shall be performed with the memory loaded with a background of zeros, then with a

background of ones, for all inputs High, then Low. Only the worst case shall be recorded.

- 6. Data retention procedure:

- (a) Write memory at  $V_{DD} = 4.5V$  with Checkerboard pattern with  $V_{IL} = 0V$  and  $V_{IH} = 3V$ .

- (b) Power down to  $V_{DD} = 2V$  for 250ms,  $V_{IN}(\overline{CS}1)=1.8V$  or  $V_{IN}(CS2)=0.2V$ .

- (c) Restore V<sub>DD</sub> to 4.5V, wait t<sub>R</sub>(operation recovery time), read memory and compare with original pattern.

- (d) Repeat the procedure with Checkerboard pattern.

- (e)  $t_B = 45$ ns for Variants 01 and 02,  $t_B = 30$ ns for Variants 03 and 04.

- (f) During power up and power down transitions,  $V_{IN}(\overline{CS}1) \ge V_{DD}$ -0.2V or  $V_{IN}(CS2) \le 0.2V$ ,  $V_{IN}(Remaining Inputs) \le 0.2V$  or  $V_{DD}$ -0.2V.

- 7. Guaranteed but not tested.

- 8. Measurements shall be performed, on a go-no-go basis, during Functional Test 4.

- 9. Measurements shall be performed during Functional Test 4 using March pattern at 4.5V and 5.5V.

- 10. Guaranteed but not tested with an output loading of 5pF.

## 2.3.2 <u>High and Low Temperatures Electrical Measurements</u>

The measurements shall be performed at  $T_{amb}$ =+125(+0-5) $^{o}$ C and  $T_{amb}$ =-55(+5-0) $^{o}$ C. The characteristics, test methods, conditions and limits shall be the same as specified for Room Temperature Electrical Measurements.

#### 2.4 PARAMETER DRIFT VALUES

Unless otherwise specified, the measurements shall be performed at  $T_{amb}$ =+22 ±3°C.

The test methods and test conditions shall be as per the corresponding test defined in Room Temperature Electrical Measurements.

The drift values ( $\Delta$ ) shall not be exceeded for each characteristic specified. The corresponding absolute limit values for each characteristic shall not be exceeded.

| Characteristics                                              | Symbols            |            | Units |       |    |

|--------------------------------------------------------------|--------------------|------------|-------|-------|----|

|                                                              |                    | Drift      | Abso  | olute |    |

|                                                              |                    | Value<br>Δ | Min   | Max   |    |

| Low Level Input Current                                      | I <sub>IL</sub>    | ±0.1       | -     | -1    | μΑ |

| High Level Input Current                                     | I <sub>IH</sub>    | ±0.1       | -     | 1     | μΑ |

| Output Leakage Current, Third<br>State, Low Level Applied 1  | I <sub>OZL1</sub>  | ±0.1       | -     | -1    | μА |

| Output Leakage Current, Third<br>State, Low Level Applied 2  | I <sub>OZL2</sub>  | ±0.1       | -     | -1    | μА |

| Output Leakage Current, Third<br>State, High Level Applied 1 | I <sub>OZH1</sub>  | ±0.1       | -     | 1     | μА |

| Output Leakage Current, Third<br>State, High Level Applied 2 | I <sub>OZH2</sub>  | ±0.1       | -     | 1     | μА |

| Low Level Output Voltage                                     | V <sub>OL</sub>    | ±100       | -     | 400   | mV |

| High Level Output Voltage                                    | V <sub>OH</sub>    | ±0.1       | 2.4   | -     | V  |

| Stand-by Supply Current 1                                    | I <sub>DDSB1</sub> | ±0.2       | -     | 2     | mA |

| Characteristics           | Symbols            |            | Units |     |    |

|---------------------------|--------------------|------------|-------|-----|----|

|                           | Drift              |            | Abso  |     |    |

|                           |                    | Value<br>Δ | Min   | Max |    |

| Stand-by Supply Current 2 | I <sub>DDSB2</sub> | ±30        | -     | 300 | μΑ |

| Data Retention Current    | I <sub>DDDR</sub>  | ±15        | -     | 150 | μΑ |

# **NOTES:**

1. Unless otherwise specified all inputs and outputs shall be tested for each characteristic.

# 2.5 <u>INTERMEDIATE AND END-POINT ELECTRICAL MEASUREMENTS</u>

Unless otherwise specified, the measurements shall be performed at  $T_{amb}$ =+22  $\pm 3^{\circ}$ C.

The test methods, test conditions and limits shall be as per the corresponding test defined in Room Temperature Electrical Measurements.

| Characteristics                                                        | Symbols            | Lin | nits       | Units |

|------------------------------------------------------------------------|--------------------|-----|------------|-------|

|                                                                        |                    | Min | Max        |       |

| Functional Test 1                                                      | -                  | -   | -          | -     |

| Functional Test 2                                                      | -                  | -   | -          | -     |

| Functional Test 3                                                      | -                  | -   | -          | -     |

| Input Clamp Voltage, to GND                                            | V <sub>IC</sub>    | -   | 300        | μΑ    |

| Low Level Input Current                                                | I <sub>IL</sub>    | -   | -1         | μΑ    |

| High Level Input Current                                               | I <sub>IH</sub>    | -   | 1          | μΑ    |

| Output Leakage Current, Third State,<br>Low Level Applied 1            | I <sub>OZL1</sub>  | -   | -1         | μΑ    |

| Output Leakage Current, Third State,<br>Low Level Applied 2            | I <sub>OZL2</sub>  | -   | -1         | μΑ    |

| Output Leakage Current, Third State,<br>High Level Applied 1           | I <sub>OZH1</sub>  | -   | 1          | μΑ    |

| Output Leakage Current, Third State,<br>High Level Applied 2           | I <sub>OZH2</sub>  | -   | 1          | μΑ    |

| Low Level Output Voltage                                               | V <sub>OL</sub>    | -   | 400        | mV    |

| High Level Output Voltage                                              | V <sub>OH</sub>    | 2.4 | -          | V     |

| Stand-by Supply Current 1                                              | I <sub>DDSB1</sub> | -   | 2          | mA    |

| Stand-by Supply Current 2                                              | I <sub>DDSB2</sub> | -   | 300        | μΑ    |

| Dynamic Operating Supply Current<br>Variants 01, 02<br>Variants 03, 04 | I <sub>CCOP</sub>  |     | 100<br>130 | mA    |

| Data Retention Current                                                 | I <sub>DDDR</sub>  | -   | 150        | μΑ    |

| Data Retention Test                                                    | -                  | -   | -          | -     |

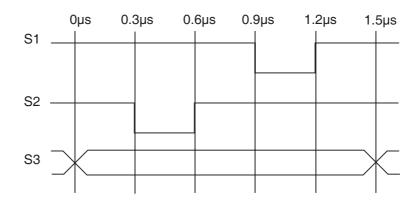

# 2.6 <u>POWER BURN-IN CONDITIONS</u>

| Characteristics                       | Symbols              | Test Conditions                                        | Units |

|---------------------------------------|----------------------|--------------------------------------------------------|-------|

| Ambient Temperature                   | T <sub>amb</sub>     | +125 (+0 -5)                                           | °C    |

| Input CS1                             | V <sub>IN</sub>      | V <sub>SS</sub>                                        | V     |

| Input CS2                             | V <sub>IN</sub>      | V <sub>DD</sub>                                        | V     |

| Inputs A0 to A16                      | V <sub>IN</sub>      | V <sub>GEN(S3)</sub> to V <sub>GEN(S19)</sub> (Note 1) | V     |

| Input OE                              | V <sub>IN</sub>      | V <sub>GEN(S1)</sub> (Note 2)                          | V     |

| Input WE                              | V <sub>IN</sub>      | V <sub>GEN(S2)</sub> (Note 2)                          | V     |

| Inputs/Outputs I/O1, I/O3, I/O5, I/O7 | V <sub>IN</sub>      | V <sub>GEN(S20)</sub> (Note 1)                         | V     |

| Inputs/Outputs I/O0, I/O2, I/O4, I/O6 | V <sub>IN</sub>      | V <sub>GEN(S21)</sub> (Note 1)                         | V     |

| Pulse Voltage                         | V <sub>GEN</sub>     | 0V to V <sub>DD</sub>                                  | V     |

| Pulse Frequency Square Wave           | f <sub>GEN(S3)</sub> | 330 ±20% (Note 4)                                      | kHz   |

| Positive Supply Voltage               | $V_{DD}$             | 5(+0.5-0)                                              | V     |

| Negative Supply Voltage               | V <sub>SS</sub>      | 0                                                      | V     |

# **NOTES:**

1.

$$f_{GEN(Sn)} = \frac{1}{2} f_{GEN(Sn-1)} \text{ for } n \ge 3$$

2. Input waveforms to indicate required timing and phase relationships:

- 3. Input Protection Resistor = Output Load =  $1k\Omega$ .

- 4. Duty Cycle =  $50 \pm 15\%$ ,  $t_r = t_f \le 100$ ns.

# 2.7 OPERATING LIFE CONDITIONS

The conditions shall be as specified for Power Burn-in.