# DOCUMENT CHANGE REQUEST

143 DCR number Changes required for: N/A Originator: P. GRIFFIN Date: 2004/10/06 Date sent: 2004/10/06 Organisation: ESA/ESTEC Status: IMPLEMENTED Title: CMOS 14-Stage Ripple-Carry Binary Counter/Divider and Oscillator, based on type 4060B Number: 1 9204/052 Issue: Other documents affected: Page: Figure 4(b) Page 32 Paragraph: Figure 4(b) Page 32 Original wording: Proposed wording: See attached 9204052 draft issue 2 para 2.3.3 note 3 Justification: Correction of error in 9204052 issue 1 Figure 4(b)-Quiescent Current Test Table. (Patterns 4 and 6 are incorrect) A copy of the figure is attached with the errors highlighted. Attachments: 9204052\_DCR1.pdf, 9204052\_DCR2.pdf, null Modifications: N/A Approval signature: Il Kiele Date signed: 2004-10-06

# ESA/SCC Detail Specification No. 9204/052

PAGE 32

ISSUE 3

## FIGURE 4 - CIRCUITS FOR ELECTRICAL MEASUREMENTS

## FIGURE 4(a) - FUNCTIONAL TEST TABLE

| PATTERN |   | PIN NUMBERS |   |   |   |    |   |   |    |                |    |    |    |    | D.C. SUPPLY |                 |

|---------|---|-------------|---|---|---|----|---|---|----|----------------|----|----|----|----|-------------|-----------------|

| No.     | 1 | 2           | 3 | 4 | 5 | 6  | 7 | 9 | 10 | 11<br>(NOTE 3) | 12 | 13 | 14 | 15 | 8           | 16              |

| 1       | 0 | 0           | 0 | 0 | 0 | 0  | 0 | 0 | 1  | 0              | 1  | 0  | 0  | 0  | 0           | V <sub>DD</sub> |

| 2       | 0 | 0           | 0 | 0 | 0 | 0  | 0 | 0 | 1  | 0.             | 0  | 0  | 0  | 0  | i           | 1               |

| 3       | 0 | 0           | 0 | 0 | 0 | 0  | 0 | 1 | 0  | 1              | 0  | 0  | 0  | 0  |             |                 |

| 4       | 0 | 0           | 0 | 0 | 0 | 0  | 0 |   |    | 0              | 1  | 0  | 0  | 0  |             |                 |

| 5       | 0 | 0           | 0 | 0 | 0 | 0  | 0 |   |    | 0              | 0  | 0  | 0  | 0  | }           |                 |

| 6       | 0 | 0           | 0 | 0 | 0 | 0  | 0 |   |    | 5461           | 0  | 0  | 0  | 0  |             |                 |

| 7       | 0 | 1           | 0 | 0 | 1 | 1  | 0 |   |    | 0              | 0  | 1  | 0  | 0  |             |                 |

| 8       | 0 | 1           | 0 | 0 | 1 | 1  | 0 |   |    | 5461           | 0  | 1  | 0  | 0  |             |                 |

| 9       | 1 | 0           | 1 | 1 | 0 | 0  | 1 |   |    | 0              | 0  | 0  | 1  | 1  |             |                 |

| 10      | 1 | 0           | 1 | 1 | 0 | 0  | 1 |   |    | 5461           | 0  | 0  | 1  | 1  |             | ļ               |

| 11      | 1 | 1           | 1 | 1 | 1 | 1  | 1 |   |    | 0              | 0  | 1  | 1  | 1  |             |                 |

| 12      | 0 | 0           | 0 | 0 | 0 | 0_ | 0 |   |    | 1              | 0  | 0  | 0  | 0  | <b>V</b>    | <b>V</b>        |

#### NOTES

- 1. Figure 4(a) illustrates one series of Test Patterns. Any other pattern series must be agreed with the Qualifying Space Agency and shall be included as an Appendix.

- 2. Logic Level Definitions:  $1 = V_{IH} = V_{DD}$ ,  $0 = V_{IL} = V_{SS}$ .

- 3. From pattern 6 onwards, the figure indicated in the "Pin 11" column is the total number of  $\phi$ 1 pulses that must be applied to obtain the indicated output conditions.

## FIGURE 4(b) - QUIESCENT CURRENT TEST TABLE

| PATTERN |   | PIN NUMBERS |   |   |    |   |   |   |    |                |    |    |    |    |      | D.C. | SUPPLY   |

|---------|---|-------------|---|---|----|---|---|---|----|----------------|----|----|----|----|------|------|----------|

| No.     | 1 | 2           | 3 | 4 | 5  | 6 | 7 | 9 | 10 | 11<br>(NOTE 3) | 12 | 13 | 14 | 15 | TEST | 8    | 16       |

| 1       | 0 | 0           | 0 | 0 | 0  | 0 | 0 | 0 | 1  | 0              | 1  | 0  | 0  | 0  |      | 0    | $V_{DD}$ |

| 2       | 0 | 0           | 0 | 0 | 0  | 0 | 0 | 0 | 1  | 0              | 0  | 0  | 0  | 0  | 1    | li   |          |

| 3       | 0 | 0           | 0 | 0 | 0  | 0 | 0 | 1 | 0  | 5461           | 0  | 0  | 0  | 0  |      |      |          |

| 4       |   | 0           | 1 | 0 | 1  | 1 | 0 |   |    | 0              | 0  | 1  | 0  | 0  | 2    |      |          |

| 5       | 0 | 1           | 0 | 0 | 1  | 1 | 0 |   |    | 5461           | 0  | 1  | 0  | 0  |      |      |          |

| 6       | 0 | •           | 0 | 1 | 0  | 0 | 1 | 1 |    | 0              | 0  | 0  | 1  | 1  | 3    |      |          |

| 7       | 1 | 0           | 1 | 1 | 0  | 0 | 1 |   |    | 5461           | 0  | 0  | 1  | 1  |      |      |          |

| 8       | 1 | 1           | 1 | 1 | 1  | 1 | 1 | 1 |    | 0              | 0  | 1  | 1  | 1  | 4    | 1 1  |          |

| 9       | 0 | 0           | 0 | 0 | 0_ | 0 | 0 |   |    | 6              | 0  | 0  | 0  | 0  | 5    | _    | <u> </u> |

## **NOTES**

- 1. Figure 4(b) illustrates one series of Test Patterns. Any other pattern series must be agreed with the Qualifying Space Agency and shall be included as an Appendix.

- 2. Logic Level Definitions:  $1 = V_{IH} = V_{DD}$ ,  $0 = V_{IL} = V_{SS}$ .

- 3. The figure indicated in the "Pin 11" column is the total number of  $\phi$ 1 pulses that must be applied to obtain the indicated output conditions.

| Characteristics                | Symbols          | MIL-STD-883 | Test Conditions                                                                                                                                                         | Lin          | Units        |   |

|--------------------------------|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|---|

|                                |                  | Test Method | Note 1                                                                                                                                                                  | Min          | Max          |   |

| Threshold Voltage<br>N-Channel | $V_{THN}$        | -           | CLR Input at Ground<br>All Other Inputs:<br>V <sub>IN</sub> =5V<br>V <sub>DD</sub> =5V, I <sub>SS</sub> =-10µA<br>T <sub>amb</sub> =+125°C<br>T <sub>amb</sub> =- 55°C  | -0.3<br>-0.7 | -3.5<br>-3.5 | V |

| Threshold Voltage<br>P-Channel | V <sub>THP</sub> | -           | CLR Input at Ground<br>All Other Inputs:<br>V <sub>IN</sub> =-5V<br>V <sub>SS</sub> =-5V, I <sub>DD</sub> =10μA<br>T <sub>amb</sub> =+125°C<br>T <sub>amb</sub> =- 55°C | 0.3<br>0.7   | 3.5<br>3.5   | V |

### 2.3.3 Notes to Electrical Measurement Tables

- Unless otherwise specified all inputs and outputs shall be tested for each characteristic, inputs not under test shall be V<sub>IN</sub> = V<sub>SS</sub> or V<sub>DD</sub> and outputs not under test shall be open.

- 2. Functional tests shall be performed to verify Truth Table with  $V_{OH} \ge V_{DD}$  -0.5V,  $V_{OL} \le 0.5$ V. The Maximum time to output comparator strobe = 300 $\mu$ s.

- 3. Quiescent Current shall be tested using the following input conditions:

- (a) Input CLR =  $V_{IH}$ ; Input CLK =  $V_{IL}$ .

- (b) Input CLR = CLK =  $V_{IL}$ .

- (c) Input CLR = V<sub>IL</sub>; 5461 pulses applied to CLK to configure outputs QE, QG, QI, QM to high level.

- (d) Input CLR =  $V_{IL}$ ; 5461 additional pulses applied to CLK to configure outputs QD, QF, QH, QJ, QL, QN to a high level.

- (e) Input CLR =  $V_{IL}$ ; 5461 additional pulses applied to CLK to configure all outputs QD to QN to a high level.

- (f) Input CLR = V<sub>IL</sub>; 1 additional pulse applied to CLK to configure all outputs QD to QN to a low level.

- 4. Interchange of forcing and measuring parameters is permitted.

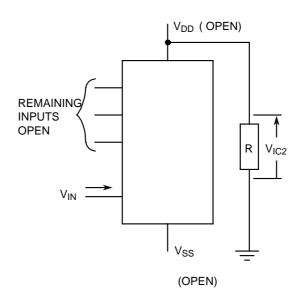

- Input Clamp Voltage 2 to V<sub>DD</sub>, V<sub>IC2</sub>, shall be tested on each input as follows:-