ESA/SCC Detail Specification No. 9202/042 PAGE 14

ISSUE 3

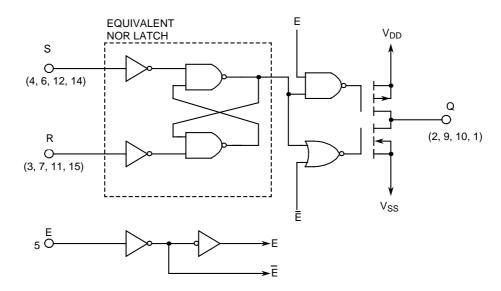

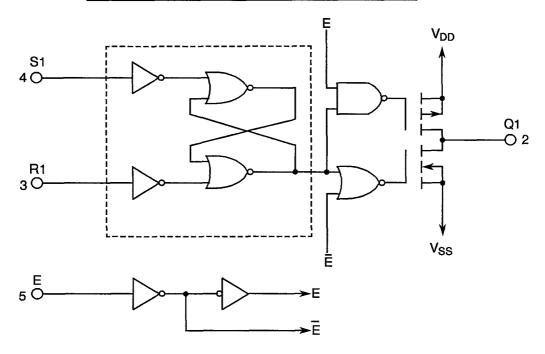

## FIGURE 3(c) - CIRCUIT SCHEMATIC (EACH LATCH)

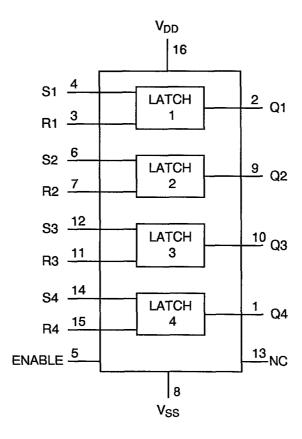

# FIGURE 3(d) - FUNCTIONAL DIAGRAM

ISSUE 2

| Symbols | Dimensions mm |       | Notes |

|---------|---------------|-------|-------|

|         | Min           | Max   | Notes |

| K       | 9 TYPICAL     |       |       |

| L       | 10            | 10.65 |       |

| M       | 0.33          | 0.43  |       |

| N       | 4.31 TYPICAL  |       |       |

#### 1.7.5 Consolidated Notes

- Index area; a notch or a dot shall be located adjacent to Pin 1 and shall be within the shaded area shown. For chip carrier packages, the index shall be as shown.

- 2. The dimension shall be measured from the seating plane to the base plane.

- 3. The true position pin spacing is 1.27mm between centrelines. Each pin centreline shall be located within  $\pm 0.13$ mm of its true longitudinal position relative to Pin 1 and the highest pin number.

- 4. The true position pin spacing is 2.54mm between centrelines. Each pin centreline shall be located within ±0.25mm of its true longitudinal position relative to Pin 1 and the highest pin number.

- 5. All terminals.

- 6. 14 spaces for flat, dual-in-line and small outline packages. 16 spaces for chip carrier packages.

- 7. Index corner only 2 dimensions.

- 8. 3 non-index corners 6 dimensions.

- 9. For all pins, either pin shape may be supplied.

### 1.8 <u>FUNCTIONAL DIAGRAM</u>

Pin numbers relate to FP, DIP and SO packages only

#### **EACH LATCH**